锁存器

SR锁存器

SR 锁存器,留意图中的输入为NOT S及NOT R

最简单的锁存器是“SR锁存器”,(又有称为“RS锁存器”),其中“S”表示“设定”(Set),“R”表示“重设”(Reset)。这种锁存器是由一对相互交错的NAND逻辑门组成。储存的比特是在输出的地方用 Q {\displaystyle Q} 表示。

一般来说,在存储模式中,输入 S ¯ ¯ --> {\displaystyle {\bar {S}}} 及 R ¯ ¯ --> {\displaystyle {\bar {R}}} 的电压都是高的,逻辑上的1(逻辑一)(换句话说,S及R的电压应该是低的,逻辑上的0(逻辑零)),而输出 Q {\displaystyle Q} 及 Q ¯ ¯ --> {\displaystyle {\bar {Q}}} 则维持其原有的数值,其中 Q ¯ ¯ --> {\displaystyle {\bar {Q}}} 为 Q {\displaystyle Q} 的相反。但当 S ¯ ¯ --> {\displaystyle {\bar {S}}} (设定)被设定为逻辑零而 R ¯ ¯ --> {\displaystyle {\bar {R}}} 是逻辑一的时候,输出 Q {\displaystyle Q} 就会变成逻辑一。之后无论 S ¯ ¯ --> {\displaystyle {\bar {S}}} 是否回复到逻辑一, Q {\displaystyle Q} 亦会维持逻辑一的状态。另一方面,如果 R ¯ ¯ --> {\displaystyle {\bar {R}}} (重设)被设定为逻辑零而 S ¯ ¯ --> {\displaystyle {\bar {S}}} 是逻辑一的时候,输出 Q {\displaystyle Q} 就会变成逻辑零。同样地,无论 R ¯ ¯ --> {\displaystyle {\bar {R}}} 是否恢复到逻辑一, Q {\displaystyle Q} 亦会维持逻辑零的状态。要注意一点就是 S ¯ ¯ --> {\displaystyle {\bar {S}}} 及 R ¯ ¯ --> {\displaystyle {\bar {R}}} 都不可以同一时间为逻辑上的0,故我们要在设计上避免这一个情况出现。

门控D锁存器

门控D锁存器由SR锁存器扩展而成,增加了两个与门,一个非门和两个输入:数据( D {\displaystyle D} )及门控( G {\displaystyle G} )。S输入端被设置为D AND G,同时R输入端被设置为 D ¯ ¯ --> {\displaystyle {\bar {D}}} AND G。当G为低电平(0)时,输出保持不变(换言之, Q next 等于Q)。当G为高电平(1)时,输出(Q)与D相同。

参考

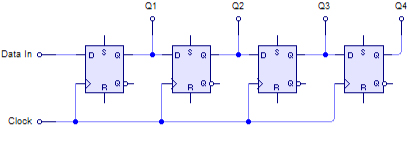

触发器

透通锁存器

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

24小时热门

推荐阅读

知识互答

关于我们

APP下载

{{item.time}} {{item.replyListShow ? '收起' : '展开'}}评论 {{curReplyId == item.id ? '取消回复' : '回复'}}