Nehalem微架构

技术特点

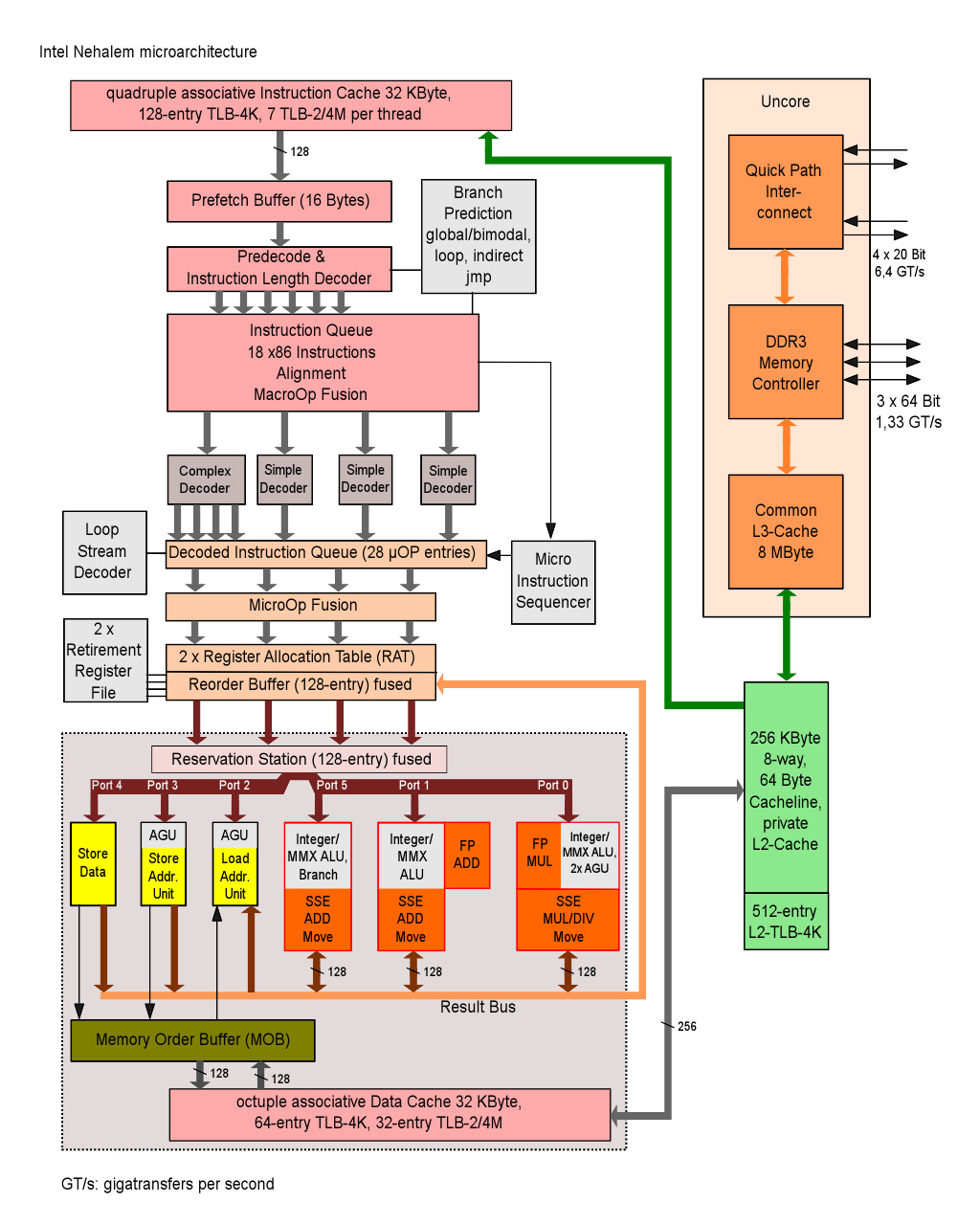

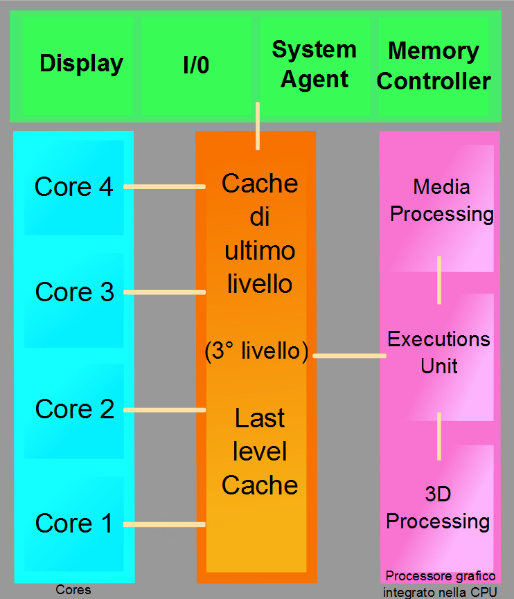

原生四核心的Nehalem微架构

集成北桥

全部型号的微处理器核心都集成了存储器控制器,一般支持双通道DDR3 SDRAM,消费级产品最高支持三通道DDR3 SDRAM,而服务器平台则可以支持四通道DDR3 SDRAM;除此以外还处理器核心还集成了PCI Express 2.0控制器。

直连式总线

从Nehalem微架构开始,Intel改用QPI/DMI直连式总线,放弃了传统的FSB。首发的Core i7使用了新的“Quick Path Interconnect”直连式总线,与AMD的HyperTransport相似。

相比FSB,每一个处理器都可以有独立的QPI通道与其他处理器连接,处理器之间不用再共享FSB带宽,并绕路到北桥才能通信。此外,QPI是双向传输 。

后来发布的Core i5、i3,处理器内部仍使用QPI,但与外部芯片组连接则使用与QPI类似但较QPI的带宽小的DMI(Direct Media Interface)总线。

随着FSB的‘卸任’,一般意义上的‘外频’概念由‘基准时钟频率’(BLCK)所替换。

模块化的多核心设计

处理器采用模块化设计 。例如核心、存储器控制器、以至输入输出接口控制器,都能够以不同的数量配搭,而且都能做到原生多核心设计。这样使得Nehalem架构的处理器产品线可以做成双核心、四核心、六核心乃至八核心、十核心(仅见于Xeon E7) ,可以使到产品更容易针对不同市场。与AMD K10微架构类似,每一个模块都可以有独立的电压和独立的时钟频率,让处理器在不同负载水平的性能最大化的同时更省电。

二级分支预测器和新的转译后备缓冲器(Translation Lookaside Buffer,TLB)。

超线程

超线程技术回归:部分处理器型号支持超线程的技术。消费级市场发售的最高六核心,十二线程,企业级的更达到八核心,十六线程甚至到后期的十核心,二十线程。不仅多线程处理能力加强,Intel认为该技术还能最多提升处理器30%的性能。

缓存

多级缓存:每核心64KB的L1缓存(32KB指令缓存+32KB数据缓存);每核心256KB的L2缓存,虽容量大小较Core微架构的小但拥有更低的读写延迟值;与AMD K10一样,Intel Nehalem微架构的处理器都内置L3缓存,每一个处理器共享最小4MB至最大12MB(企业级处理器更达到30MB)。

性能、电源管理

性能动态调节和电源管理:中高级型号的处理器会支持Turbo Boost动态时钟频率调整技术,倘若有程序使用较多的处理器负载,处理器的频率可以按步骤提升,此外,可以自动往上提升倍频 该功能基本不需要操作系统的支持,完全由硬件监控 。除了时钟频率管理,电源管理方面引入Power Gates技术,核心闲置的时候可被关闭。对比上一代的Core架构,的核心电阻可以被关闭,电流可以完全不通过核心。各个处理器核心可运作于不同的频率和电压 。Turbo Boost及Power Gates功能都是由一个单元提供,占去大约一百万个晶体管 。而AMD K10及后来的改进版K10.5,核心必须手动才能关闭。

指令集

指令集更新:SIMD指令SSE4的版本会提升为SSE 4.2,SSE4.2在SSE4.1(于Core架构上)的基础上新增了7条指令 ;引入第二代Intel虚拟化技术,支持EPT(Extended Page Table,扩展标签页表)、VPIDs(virtual processor identifiers,虚拟处理器标识)以及非屏蔽中断窗口退出(non-maskable interrupt-window exiting)。 Intel Nehalem架构的原子操作延时降低了50%,在试图限制原子的开销上。

搭配芯片组

芯片组方面,Intel推出了5系列芯片组与之搭配,桌面平台有P5X、H5X、X5X等系列型号,其中P5X、H5X系列型号采用LGA1156插座,X5X采用LGA1366插座。代号Bloomfield的Core i7和后期第二批的Intel X58芯片组(允许更变倍频)的组合再次提升Intel平台的超频极限。核心代号Lynnfield的Core i5所使用的芯片组,更名为“PCH”(Platform Controller Hub,PCH,集成了一部分北桥和整个南桥),替换以往分离的北桥芯片和南桥芯片,成为单片机组。 早期,处理器核心的电压与系统存储器同步。此前,Intel官方表示首批处理器产品会支持DDR3-800和DDR3-1066规格的存储器。对于DDR3-1333,由于处理器只可以接受较低的电压水平(限制在1.65V或以下),高速的存储器意味着需要较高的电压,所以此规格的官方支持仍然存在疑问 。后来第二批X58芯片组主机版上,处理器核心电压与系统存储器电压可以实现异步,方便用家超频 。另外,原先只有XE版本处理器可以调整存储器频率。后来Intel修改为所有上市的Core i7处理器,均可以修改存储器和QPI总线的频率 。

性能和能耗之改进

尽管核心面积比Core架构要大不少,性能较Core架构系列则仍大幅提升,并没有令市场期望失望。

与Core架构的45纳米制程版本Core相比,Nehalem架构:

在相同的能耗下比Core架构的单线程性能高出10%至100%;

同样的性能下的能耗平均比Core架构的低30%;

每核心每时钟周期的性能平均比上代架构高12%至20%。

核心及其步进

极致性能级别的处理器无倍频限制;

全部微处理器使用133MHz的基准时钟频率。

处理器列表

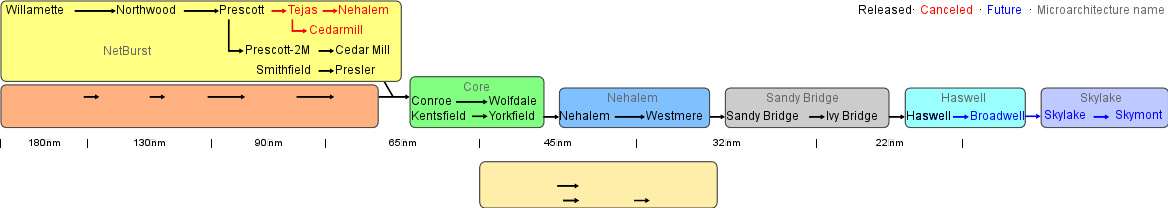

继任微架构

Intel遵循Tick-Tock策略,于2011年第一季度发布了Intel Sandy Bridge微架构,正式替换Intel Nehalem微架构以及其制程改进版Intel Westmere微架构。

Intel的微处理器架构路线图,从 NetBurst 以及 P6 至 Skylake

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

24小时热门

推荐阅读

知识互答

关于我们

APP下载

{{item.time}} {{item.replyListShow ? '收起' : '展开'}}评论 {{curReplyId == item.id ? '取消回复' : '回复'}}